Docente:

Giuseppe Scollo

Università di Catania

Facoltà di Scienze Matematiche, Fisiche e Naturali

Corso di Laurea in Informatica, I livello, AA 2009-10

elaborazione sequenziale di un programma residente in memoria

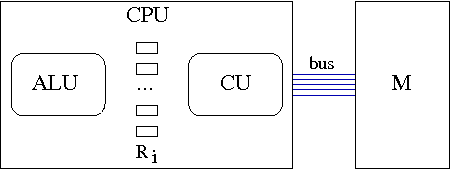

CPU: Central Processing Unit, o processore, consta di:

memoria: ospita il programma in esecuzione e i dati

bus: canale veloce di comunicazione (throughput : ∼ 100 MB/s)

architettura Von Neumann

registri, due categorie:

generici: per gli operandi di operazioni dell'ALU

speciali: di pertinenza dell'Unità di Controllo:

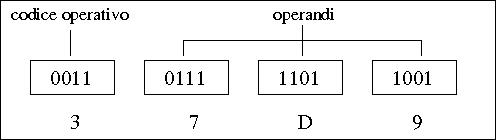

linguaggio macchina: insieme delle istruzioni accettate dalla CPU, in una data codifica

formato binario delle istruzioni:

due tipologie di linguaggi macchina (e di architettura della CPU):

classificazione del repertorio di istruzioni macchina:

prelievo:

dell'istruzione dall'indirizzo contenuto nel PC

suo trasferimento nell'IR

incremento del PC

decodifica:

dell'istruzione nell'IR

esecuzione: dell'istruzione decodificata

comunicazione mediante controller

memory-mapped I/O : comunicazione CPU-controller mediante istruzioni di trasferimento dati a indirizzi riservati (porte di I/O )

DMA (direct memory access):

bps (bits per second): velocità di trasferimento dei bit fra due dispositivi

tipi di canale di comunicazione:

modem (modulatore-demodulatore):

architettura biprocessore:

con due processori in pipeline ("incanalati") si anticipa il prelievo dell'istruzione successiva (pre-fetch ) da parte di uno dei due, mentre l'altro decodifica l'istruzione corrente

la limitata capacità del bus ne fa il collo di bottiglia dell'architettura Von Neumann

le architetture multiprocessore risultano efficaci all'accelerazione dell'esecuzione di algoritmi paralleli, grazie anche alla disponibilità di più canali di comunicazione delle istruzioni e/o dei dati

architetture sincrone:

architetture asincrone: